## 2012 Spintronics Workshop on LSI

June 11, 2012, 19:30 - 22:45

(Onsite registration 19:00-)

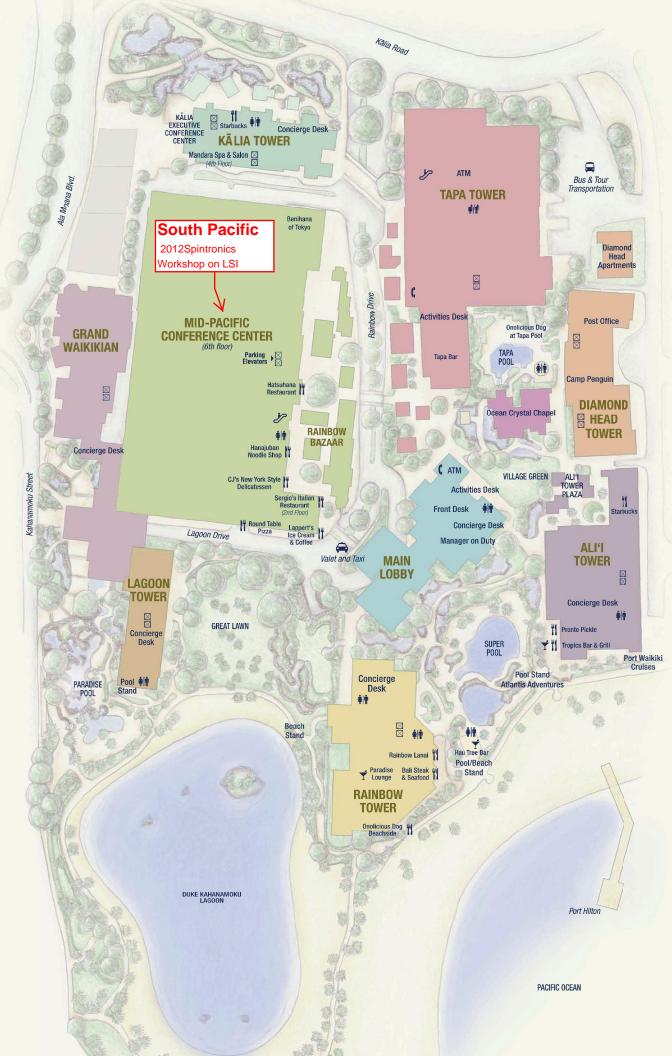

Mid-Pacific Conference Center 2nd floor / Room: South Pacific

Hilton Hawaiian Village, Honolulu, Hawaii

## **General Information**

The 2012 Spintronics Workshop on LSI will be held at Hilton Hawaiian Village, Honolulu, Hawaii, on June 11, 2012, just prior to the VLSI Symposium on Technology as a Satellite Workshop of the 2012 VLSI Symposia for the 2nd time. The workshop will focus on spintronics-based LSI technologies for high performance and ultra low power systems. Seven papers will be presented from invited speakers. The workshop is sponsored by Center for Spintronics Integrated Systems (CSIS), Tohoku University, which has been conducting the FIRST program supported by JSPS.

## Registration

The workshop fee is free of charge. Onsite registration is required. (at the entrance of Room "South Pacific" from 19:00.)

## PROGRAM

| <b>Opening</b>                       | <b>Opening Remarks :</b>                                                                                                |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 19:30 - 19:50                        | Hideo Ohno (Tohoku University, Workshop Program Chair)                                                                  |

| <b>Invited talk</b>                  | Commercial ST-MRAM Development: Recent Results and Outlook                                                              |

| 19:50 - 20:15                        | Jon Slaughter (Everspin Technologies)                                                                                   |

| <b>Invited talk</b> 20:15 - 20:40    | Magnetic Random Access Memory Current Status and Perspectives<br>Janusz Nowak (IBM)                                     |

| <b>Invited talk</b>                  | Progress and Challenges in Scalable STT-MRAM                                                                            |

| 20:40 - 21:05                        | Jeong Heon Park (Samsung)                                                                                               |

| <b>Invited talk</b><br>21:05 - 21:30 | Restructuring of Memory Hierarchy in Computing System with STT-MRAM<br>Technologies<br>Tetsuo Endoh (Tohoku University) |

| <b>Invited talk</b>                  | STTRAM for Embedded Memory: A Model Study                                                                               |

| 21:30 - 21:55                        | Arijit Raychowdhury (Intel)                                                                                             |

| <b>Invited talk</b><br>21:55 - 22:20 | Embedded STT-MRAM: Recent Progress as an Application-Aware Technolo-<br>gy<br>Seung Kang (Qualcomm)                     |

| <b>Invited talk</b><br>22:20 - 22:45 | Challenge of Nonvolatile Logic-in-Memory Architecture Towards Cool LSI<br>Chips<br>Takahiro Hanyu (Tohoku University)   |

Program Chair: Hideo Ohno (Tohoku University)

Program Committee: Philip Wong (Stanford University, Executive Committee Member of the 2012 Symposia on VLSI Technology and Circuits)

Hitoshi Wakabayashi (Sony, Symposium Co-Chair of the 2012 Symposium on VLSI Technology)

Takahiro Hanyu (Tohoku University)

Tetsuo Endoh (Tohoku University)

Secretary:

Naoki Kasai (Tohoku University, Program Committee Member of the 2012 Symposium on VLSI Technology), e-mail:sien@csis.tohoku.ac.jp Secretariat: Secretariat for VLSI Symposia (Japan), c/o ICS Convention Design, Inc.

Tel: +81-3-3219-3541, Fax: +81-3-3219-3577, e-mail: vlsisymp@ics-inc.co.jp