Technology, Manufacturing and Markets of Magnetoresistive Random Access Memory (MRAM)

**Brad Engel, VP- Product Development & Quality**

## Everspin – Electron Spin is Forever

#### Industry-first and leading MRAM supplier

- Technology leader in Toggle MRAM and ST-MRAM

- Shipped over 2.5M units with over 300 active customers to date

- > Over 15 years of design and production experience with MRAM

#### Break through non-volatile memory products and IP

- > 70 Products in 3 Memory Families

- Asynchronous x8, x16 and Serial SPI

600 Active Patents and Applications WW 176 Issued / 47 Pending US Patents

□ Backed by leading VC Investors (Spin-out from Freescale in June, 2008)

#### Global Footprint

- > Headquarters: Chandler, AZ, USA

- > Manufacturing: USA, Singapore, Thailand, China Design Center: Austin, TX, USA

Sales Offices: USA, Europe, China, Japan Design Center: Austin, TX, USA

# What is MRAM Technology?

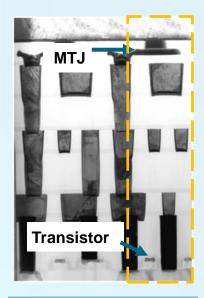

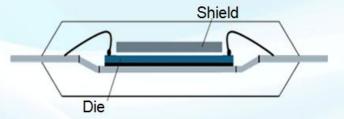

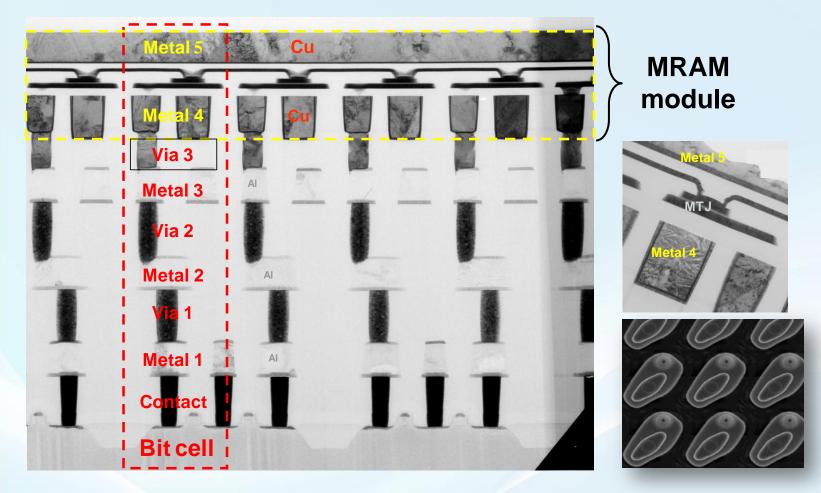

**Cross-sectional view**

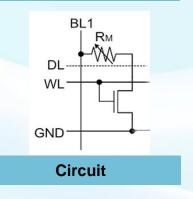

- □ Simple 1 transistor + 1 MTJ memory cell

- Magnetic polarization stores data

- Resistance levels represent bit values compared to electron charge levels

- Highly reliable non-volatile memory

- Unlimited cycling endurance

- Low latency enabling instant on/off

low resistance

- magnetic layer 1 free layer

- tunnel barrier

magnetic layer 2 fixed layer

high resistance

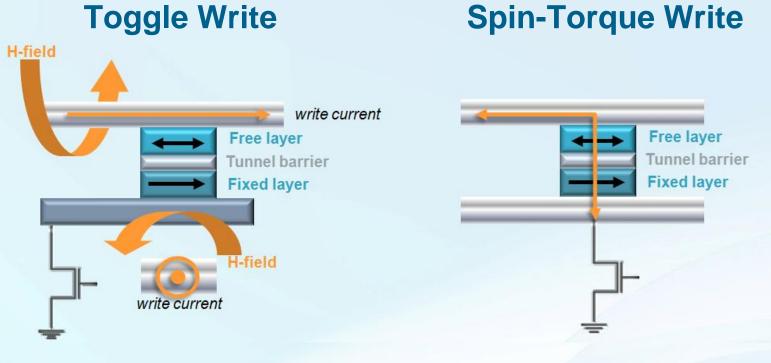

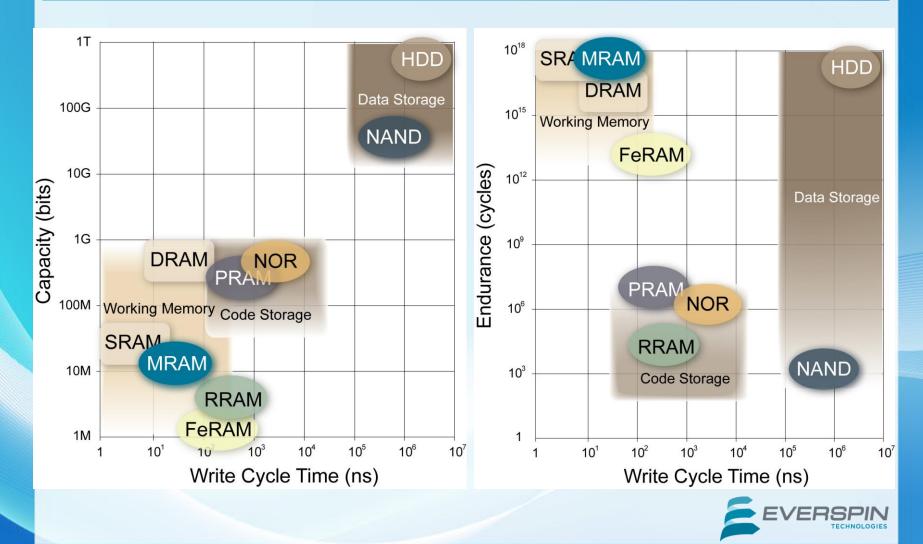

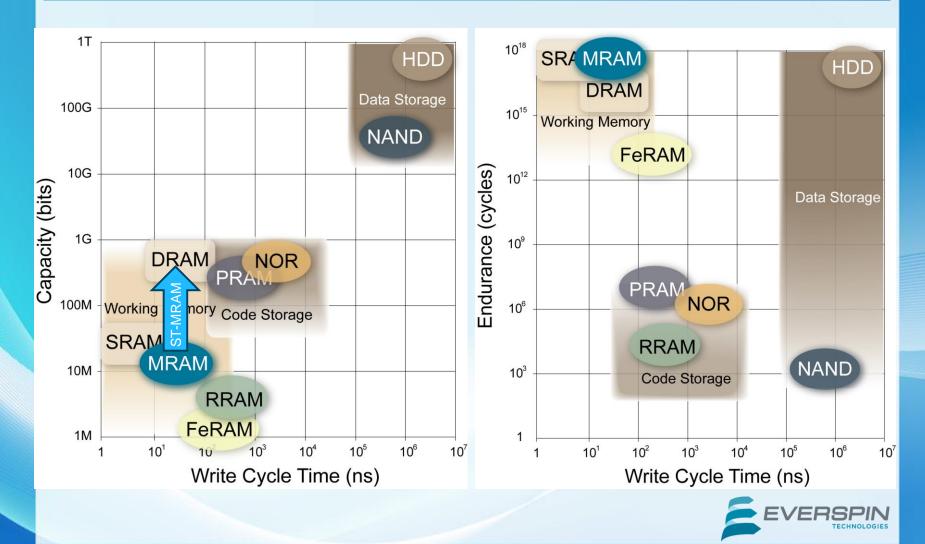

### MRAM - Technology Comparison

- Write accomplished by magnetic fields from current passing through bit and word lines.

- □ In volume production

- Write accomplished by spin polarized current passing through the MTJ.

- In development

# Everspin MRAM Advantages

| Parameter                              | Capability                                                                                                                           |  |  |  |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Non-volatile<br>capability             | Data retention of the bit cell > 20 years                                                                                            |  |  |  |  |  |

| Performance                            | Symmetric read/write – 35ns / 40MHz Serial                                                                                           |  |  |  |  |  |

| Endurance                              | Unlimited cycling endurance                                                                                                          |  |  |  |  |  |

| CMOS integration                       | Easily integrates into back-end process<br>Compatible with embedded designs → No effect on CMOS<br>Allows for flexible manufacturing |  |  |  |  |  |

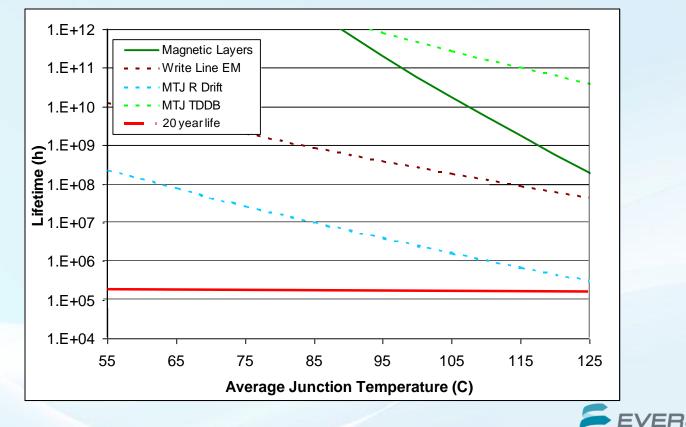

| Temperature range<br>High Temp Storage | -40°C < T < 150°C operation demonstrated<br>Intrinsic reliability > 20 years lifetime at 125°C                                       |  |  |  |  |  |

| Soft error immunity                    | Alpha radiation soft error rate too low to measure (<0.1 FIT per Mb) – Everspin partners offer radiation hardened MRAM               |  |  |  |  |  |

| Environmentally friendly               | No battery/caps, RoHS/REACH compliant, instant-on                                                                                    |  |  |  |  |  |

# How is MRAM made?

#### Leverage CMOS semiconductor ecosystem

- Everspin MRAM layer added to standard CMOS

- Standard packages with protective internal shield

#### Common standard package types

Drop in replacement fits footprints for existing printed circuit board designs

# Pin for Pin functionally equivalent > BBSRAM, SPI NVM, nvSRAM and FeRAM

### **Memory Performance**

© Everspin Technologies, Inc. 2011

### **Memory Performance**

© Everspin Technologies, Inc. 2011

### **Current Toggle MRAM Products**

#### 16-bit I/O

| Part Number | <u>Density</u> | <b>Configuration</b> | <u>Temp</u> |

|-------------|----------------|----------------------|-------------|

| MR4A16B     | 16Mb           | 1M x 16              | C,I,A       |

| MR2A16A     | 4Mb            | 256K x 16            | C,I,E,A     |

| MR0A16A     | 1Mb            | 64K x 16             | C,I,E,A     |

| 8-bit I/O   |                |                      |             |

|-------------|----------------|----------------------|-------------|

| Part Number | <u>Density</u> | <b>Configuration</b> | <u>Temp</u> |

| MR4A08B     | 16Mb           | 2M x 8               | C,I,A       |

| MR2A08A     | 4Mb            | 512K x 8             | C,I         |

| MR0A08B     | 1Mb            | 128K x 8             | C,I         |

| MR256A08B   | 256Kb          | 32K x 8              | C,I         |

| MR0D08B     | 1Mb            | 128K x 8, 1.8v I/O   | С           |

| MR256D08    | 256Kb          | 32K x 8, 1.8v I/O    | С           |

| <u>Density</u> | <b>Configuration</b> | <u>Temp</u>            |

|----------------|----------------------|------------------------|

| 4Mb            | 512K x 8             | I, A                   |

| 1Mb            | 128K x 8             | I, A                   |

| 256Kb          | 32K x 8              | I, A                   |

|                | 4Mb<br>1Mb           | 4Mb512K x 81Mb128K x 8 |

#### 48-BGA

- > x8 Asynchronous parallel I/O

- x16 Asynchronous parallel I/O

- x8 Asynchronous parallel 1.8V I/O

#### 44-TSOPII, 54-TSOP

- > x8 Asynchronous parallel I/O

- x16 Asynchronous parallel I/O

#### 8-DFN

- - SPI-compatible serial I/O

- > 40 MHz; No write delay

#### 32-SOIC

x8 Asynchronous parallel I/O

| Temperatures |                |

|--------------|----------------|

| Commercial   | 0 to +70 °C    |

| Industrial   | -40 to +85 ⁰C  |

| Extended     | -40 to +105 °C |

| Automotive   | -40 to +125 ℃  |

### **MRAM Markets & Applications**

#### **Storage Systems & Servers**

#### **Industrial Automation & Robotics**

#### **Automotive & Transportation**

#### **Telecom & Datacom**

#### **Energy Management**

#### **Consumer, POS, Gaming**

Logos, trademarks, images and copyright references are the property of the respective companies noted.

© Everspin Technologies, Inc. 2011

# Toggle MRAM Used by Top Companies

Siemens Recognizes Everspin Technologies for Perfect MRAM Quality - May, 2009 "After two years of high volume production and more than 100K systems in the field, we are very happy with the perfect quality and reliability of Everspin's products in our industrial automation systems" http://www.semiconductor.net/article/CA6658902.html

Everspin's automotive-temperature MRAM meets harsh environment demands in BMW S1000 RR racing bike

Everspin introduces AEC-Q100 MRAM products to serve broad automotive applications; 4Mb MRAM stores critical calibration data for BMW Motorsport Super Bike

Everspin Technologies' MRAM Selected by Emerson Network Power to Deliver Critical Storage for Industrial Computing Boards

Non-volatile MRAM technology provides a robust, reliable memory solution for VME and Compact PCI boards.

Everspin Technologies to provide Airbus with MRAM products for advance wide body aircraft

Flight Control Computer on A350 XQB aircraft uses MRAM for critical program and data storage in extreme environment applications.

Logos, trademarks, images and copyright references are the property of the respective companies noted.

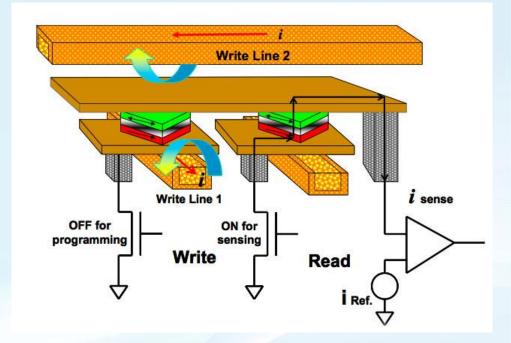

# **MRAM Writes and Reads**

- Write Current Flows Down Write Line 1 & 2

- Magnetic Tunnel Junction (MTJ) At Cross-Point Is Polarized

- Polarization State Is Read By Selecting Pass Transistor to Sense Resistance of Specific MTJ

# **MRAM Integration**

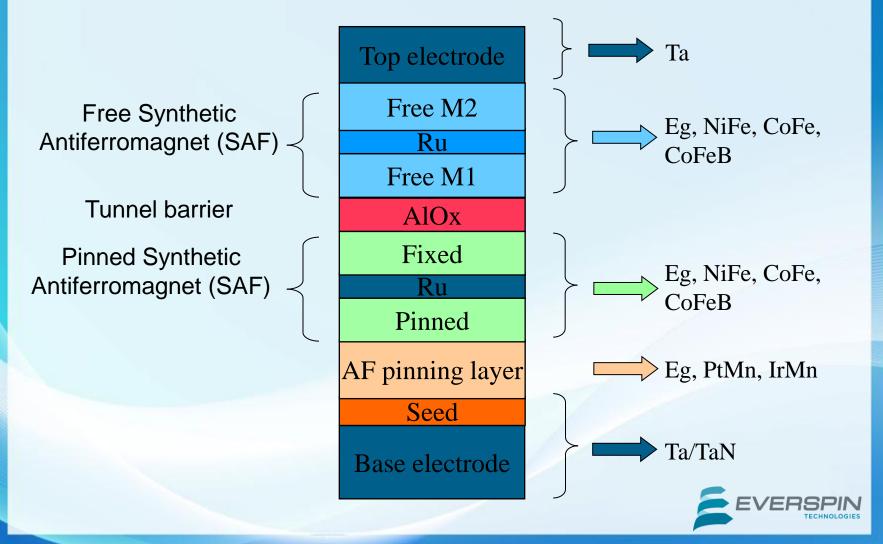

### **MTJ Bit Materials**

## **MTJ Vertical Profile**

TECHNOLOGIES

#### Ultra-thin layers require precision control for manufacturing

|                | Top electrode    |                    |      |

|----------------|------------------|--------------------|------|

| Turnel herrier | Cap layer        |                    |      |

| Tunnel barrier | Free layer       | CONSTRUCTIONS OF I |      |

|                | Fixed layer      |                    |      |

|                | Pinning layer    |                    |      |

|                | Bottom electrode |                    |      |

|                |                  |                    | EVER |

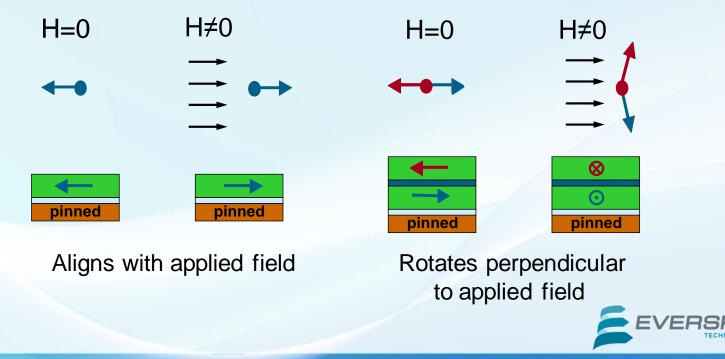

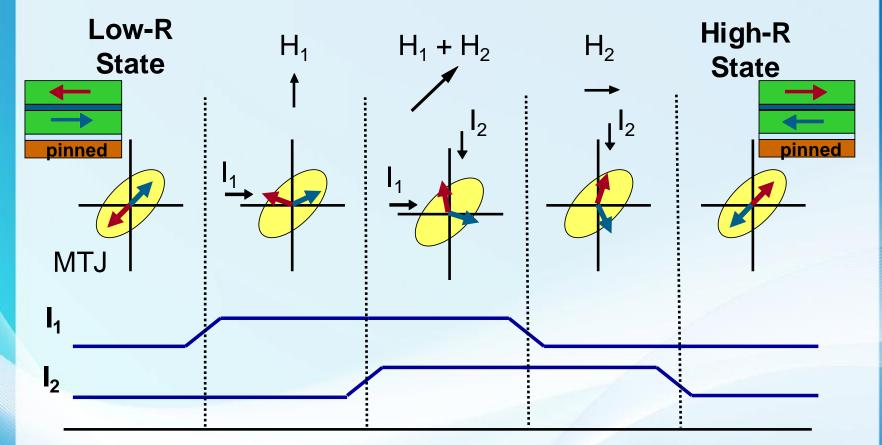

## Toggle MRAM: Write Mechanism

- Toggle MRAM is a unique approach that provides both robust switching performance and manufacturability

- > Response of synthetic antiferromagnetic free layer is the key.

Conventional MRAM Single Layer Toggle MRAM Synthetic Antiferromagnet

# **Toggle Write Operation**

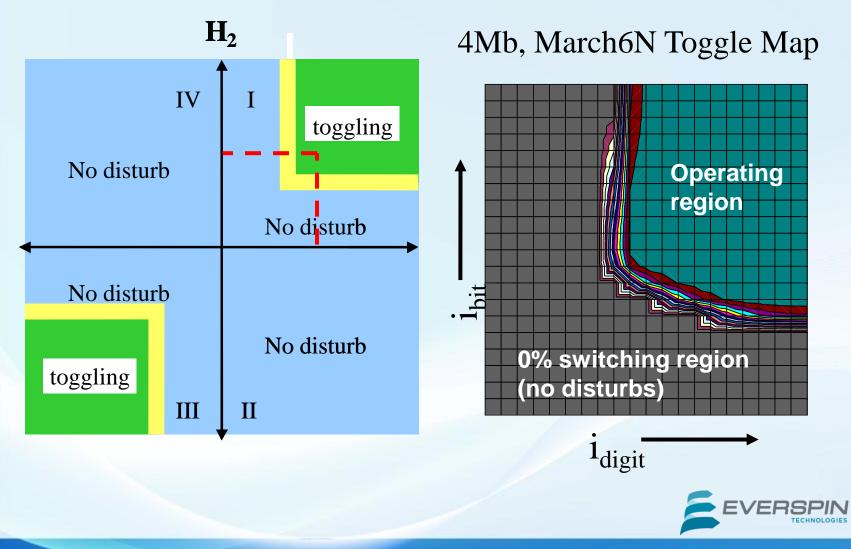

Advantages: Eliminates disturb - Large operating window

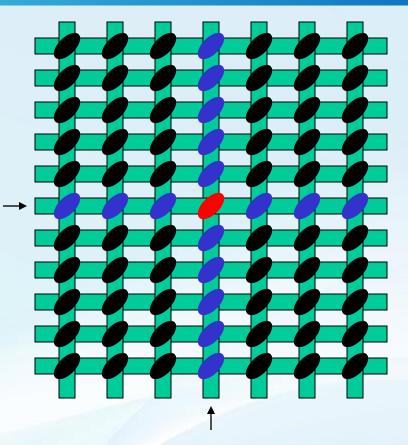

#### **Robust Toggle-Bit Selection**

# Robust bit disturb margin

All bits along ½-selected current lines have increased energy barrier during programming

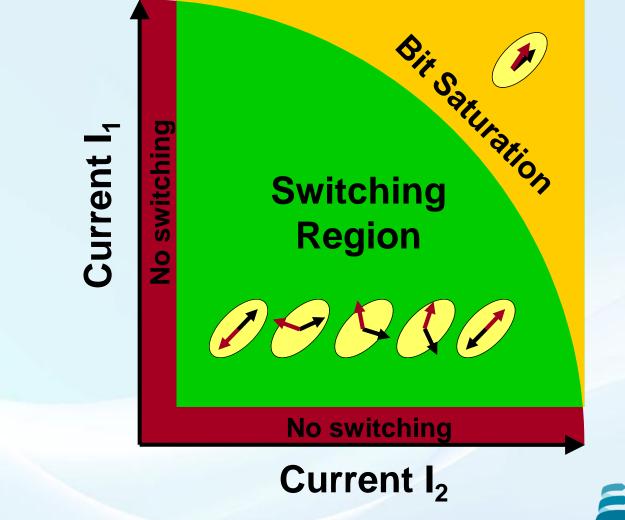

### **Toggle Switching Characteristics**

### **Toggle-bit Array Characteristics**

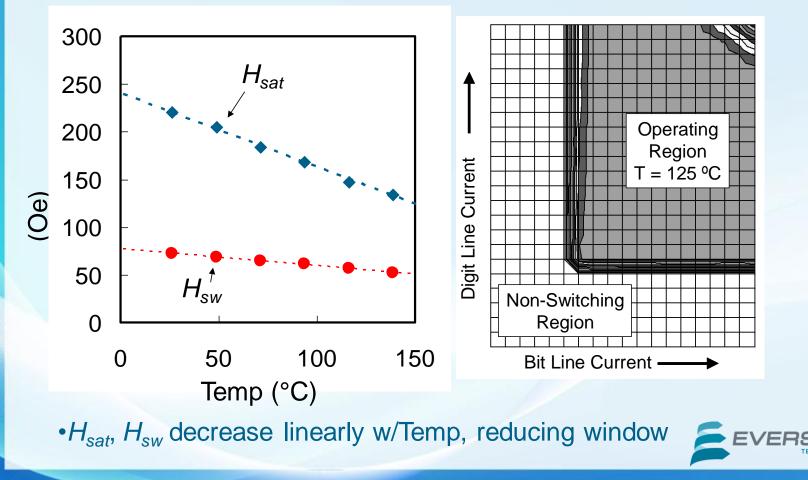

## Write Operating Region at 125 °C

□ Large write window at Automotive temperatures

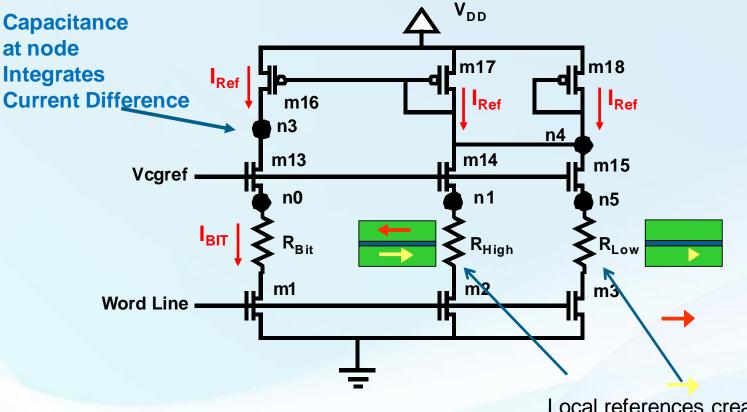

# **Read Sense Amplifier**

$I_{\rm Ref} = (I_{\rm High} + I_{\rm Low})/2$

Local references created from two MTJ: one high and one low resistance state

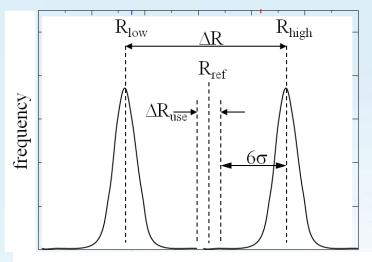

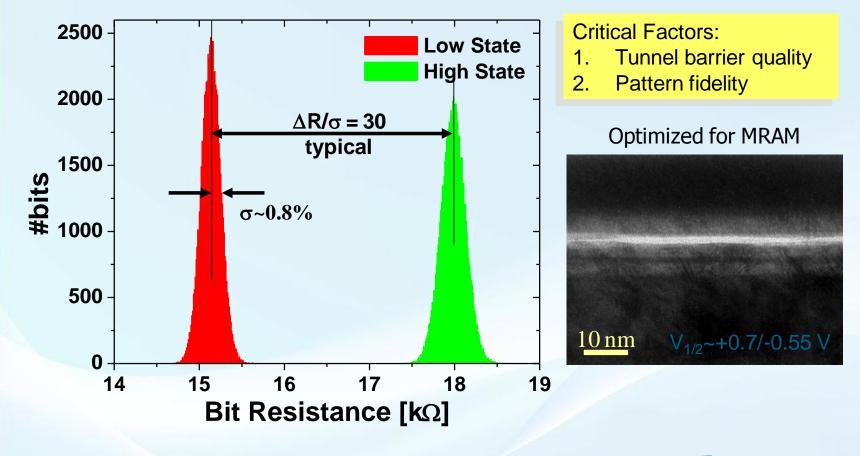

#### Magnetoresistance and Distributions

$MR = \Delta R/R_{low} , \Delta R = R_{high} - R_{low}$

- $\Box Signal = R_{cell} R_{ref}$

- >  $\frac{1}{2}$  of  $\Delta R$  available for sensing

#### Circuit works at finite bias

MR is reduced by bias dependence of MR

# Must sense all bits in the array

Circuit must work with bits in tails of the R distribution

Resistance distribution reduces useable MR.

For six-sigma yield in the array, need:  $\Delta R/2 > 6\sigma$

#### Array: R<sub>cell</sub> Histogram

Cell Resistance (k $\Omega$ )

### **Read Distribution within an Array**

#### MTJ Deposition on 200mm Wafers

#### Measured uniformity—200 mm

|      | $MR=45\%, \sigma=2\%$ |      |      |      |      |      |      | RA=10.4 kΩ- $\mu$ m <sup>2</sup> , σ=6% |      |      | 6%   |      |      |      |      |

|------|-----------------------|------|------|------|------|------|------|-----------------------------------------|------|------|------|------|------|------|------|

|      | 43.9                  | 44.5 | 44.6 | 44.8 | 44.5 | 43.1 |      |                                         | 11.3 | 11.0 | 10.5 | 10.5 | 10.9 | 12.3 |      |

| 44.4 | 45.0                  | 45.2 | 46.0 | 45.8 | 46.0 | 44.6 | 43.1 | 11.7                                    | 10.3 | 9.74 | 9.88 | 9.65 | 9.80 | 10.2 | 11.5 |

| 44.1 | 45.4                  | 42.9 | 45.6 |      | 45.6 | 45.8 | 44.5 | 10.3                                    | 9.54 | 10.9 | 10.6 |      | 10.3 | 9.74 | 10.5 |

| 44.5 | 46.1                  | 44.3 | 45.1 | 45.5 | 45.8 | 46.0 | 45.0 | 10.1                                    | 9.68 | 10.4 | 10.8 | 10.8 | 10.7 | 9.85 | 10.7 |

| 44.5 | 45.8                  | 43.4 | 45.4 | 45.9 | 45.7 | 45.9 | 44.7 |                                         | 9.80 | 10.9 | 10.5 | 10.8 | 10.5 | 9.86 | 10.2 |

| 44.2 | 45.3                  | 45.7 | 45.5 | 43.9 | 45.8 | 45.4 | 44.0 | 10.3                                    | 9.45 | 10.1 | 10.4 | 10.6 | 9.87 | 9.62 | 10.9 |

|      | 44.1                  | 45.3 | 45.9 | 45.6 | 45.0 | 44.7 |      |                                         | 10.2 | 9.52 | 9.43 | 9.56 | 9.59 | 10.2 |      |

|      |                       | 43.4 | 44.0 | 44.8 | 44.1 |      |      |                                         |      | 11.2 | 10.2 | 10.4 | 11.0 |      |      |

Manufacturable wafer level uniformity and wafer-to-wafer repeatabilityoptimization of deposition tool, process, and material stack

### Toggle MRAM High Reliability

# Predicted lifetime from accelerated testing Robust reliability at Automotive temperatures

### Summary

#### MRAM is a highly reliable, high-performance, nonvolatile memory IC, with unlimited endurance

Has the unique characteristics of a working memory while providing non-volatility

#### Current MRAM products are used in a wide variety of applications

Data Storage, Industrial Control, Medical Systems, Transportation, Metering and Gaming

#### Everspin Continues MRAM leadership:

- Expanding MRAM into new markets and applications

- On track to deliver the industry's first ST-MRAM